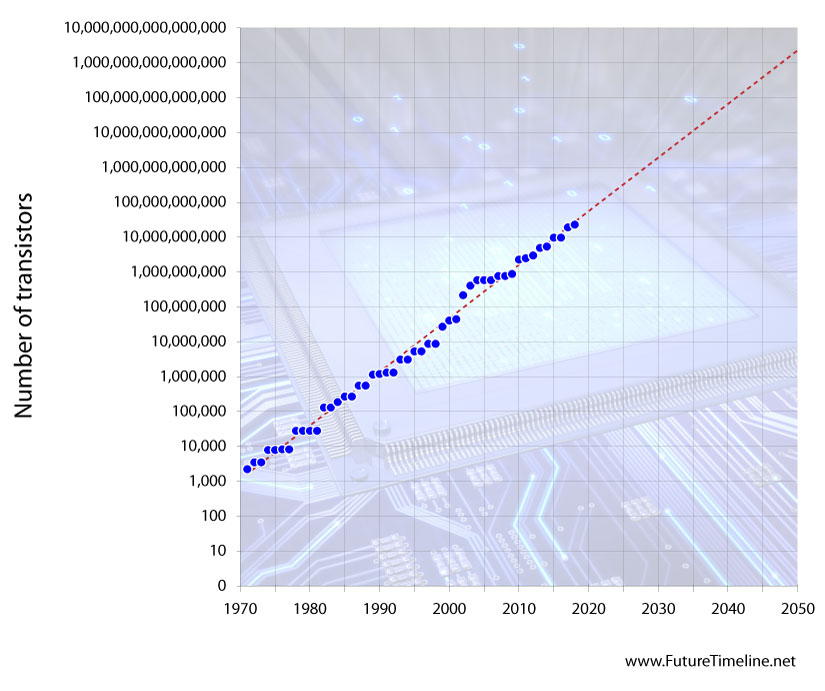

31st August 2020 50-fold increase in transistor density is possible by 2030 Intel's Chief Architect, Raja Koduri, has presented a roadmap for increasing the number of transistors able to fit on a chip by a factor of 50. During a keynote presentation at this year's Hot Chips conference (held virtually), he described the ways in which computer technology can continue to shrink over the next 10 years – helping to sustain the famous trend known as Moore's Law. For many years, analysts have been predicting the end of Moore's Law, with concerns that the exponential growth in computer processing power may be slowing or about to reach a fundamental limit. However, thanks to new innovations in processor architecture and power consumption, Mr. Koduri is adamant that plenty of life remains in this trend. Top-of-the-range processors currently hold about 30 to 40 billion transistors. If Mr. Koduri's prediction is right, the first chips with over a trillion transistors may emerge by the end of this decade (although, strictly speaking, Cerebras Systems achieved that particular milestone last year; their chip is, however, spread over a much larger area than conventional form factors). "We firmly believe there is a lot more transistor density scaling to come," said Koduri.

Koduri outlined several key advances that could shape the next 10 years of computer processor development. The first step would focus on current FinFET transistor technology (10nm), with further improvements in pitch scaling, tripling its density. The FinFET architecture would then morph into nanowire architecture, he explained, doubling the previous transistor count for a combined six-fold increase. NMOS and PMOS nanowires could then be stacked on top of each other, for another doubling, or a cumulative 12-fold increase. These technologies are already being researched, he added. Regular pitch scaling would no longer be feasible beyond this point. Instead, die stacking and packaging technologies would provide the increased density. So the next step may involve wafer-to-wafer stacking, enabling a further 2x boost in transistor count, or a cumulative 24-fold increase. The final step, Koduri predicted, could be die-to-wafer stacking. This would provide yet another doubling. All of these five steps are shown in the animation below. Combined, they could increase the number of transistors being placed on computer chips almost 50-fold compared to today. "I'd like to remind everyone that these are not just cartoons on paper," said Koduri. "Everything I've described here today is happening in labs across the world. The vision will play out over time – maybe a decade or more – but it will play out."

--- Follow us: Twitter | Facebook | Instagram | YouTube

Comments »

If you enjoyed this article, please consider sharing it:

|